Mise en garde : En partie 1-4-1, nous avons détaillé les dynamiques radiatives dans le Géoespace et notamment leurs variations extrêmes. Dans cette partie 1-4-3-1, nous nous attachons à comprendre les effets induits par ces radiations sur l’électronique de vol, c’est à dire à l’échelle microscopique des composants. Un prochain article à suivre (1-4-3-2) détaillera les manifestations de ces effets radiatifs au niveau systémique (anomalies, incidents, pannes dans les satellites et les aéronefs à haute altitude). Comme tous les articles en partie 1, nous cherchons à en décrire les logiques physiques, tous les impacts et toutes les stratégies de résilience face à ces phénomènes radiatifs seront vus en partie 2 et 3.

Introduction

10 milliards de $ de dégâts, c’est le montant approximatif que coûte l’activité solaire sur les satellites chaque année (même s’il est difficile de connaître exactement ce coût puisque les opérateurs sont réticents à communiquer leurs défaillances dans un contexte très concurrentiel). Une des principales causes de ces coûts, environ 35 à 50%, sont les pannes liées aux rayons ionisants venus de l’espace, notamment du soleil, sur l’électronique embarquée.

Comme nous l’avons vu dans l’article précédant, l’environnement spatial, source de radiations pour les satellites, est dominé par les ions lourds, les protons et les électrons tandis que l’environnement atmosphérique des avions long courrier est dominé par les effets ionisants des neutrons dit « thermiques ». Avec la miniaturisation constante des appareils à semiconducteurs, les rayonnements ionisants prennent de plus en plus d’importance dans les causes d’anomalies des satellites mais aussi dans celle des aéronefs à haute altitude.

Afin d’améliorer la compréhension des phénomènes induits par ces radiations, nous nous sommes cantonnés à une approche physique très qualitative, mais permettant in fine de comprendre la plupart des effets radiatifs microscopiques communément désignés par la communauté scientifique et, mieux encore, de pouvoir comprendre les benchmarks des composants électroniques face aux impacts radiatifs des particules énergétiques venues de l’espace.

Notions physiques sur les semiconducteurs

Conductivité électrique des semiconducteurs

Un semiconducteur, comme le silicium, est un matériau qui n’est ni tout à fait conducteur d’électricité, ni tout à fait isolant. C’est à dire qu’il possède la propriété qu’il peut être soit conducteur, soit isolant, dans certaines conditions (tensions appliquées, champs électromagnétiques, énergie, chaleur, lumière, déformation mécanique).

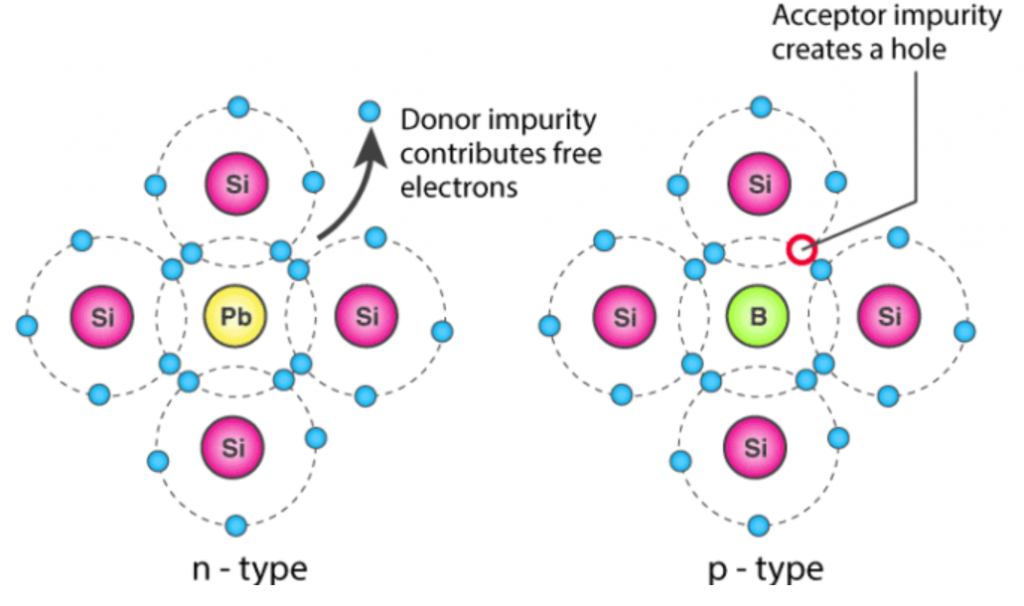

Dopage et zones de type-n et de type-p

Pour donner cette propriété au matériau semiconducteur, il est utilisé la technique du dopage, où on créé des impuretés dans une grille pure de silicium (en injectant des atomes autres que le silicium qui ont plus ou moins d’électrons). Ces impuretés donnent soit des structures avec des trous (où il manque des électrons mobiles et qu’on peut simplifier comme étant des particules à charge positive – semiconducteurs de type-p) soit des structures avec un excès d’électrons mobiles (qui donnent l’effet d’être chargée négativement donc des semiconducteurs de type-n).

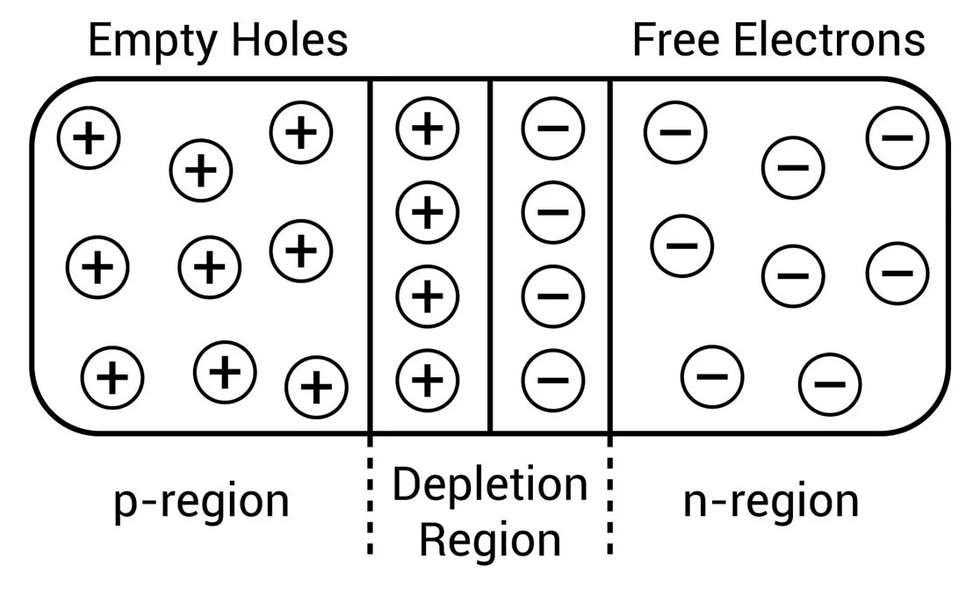

Zone de déplétion (jonction p-n)

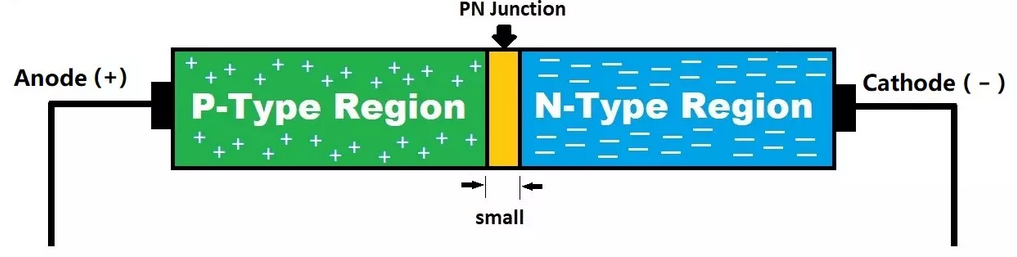

Lorsqu’on met en contact ces deux zones, il se forme une région de déplétion appelée aussi jonction p-n, où les électrons se sont recombinés avec les trous ce qui forme donc une barrière isolante entre les zone n et p (et où il n’y a donc aucune charge mobile).

Cependant, si on applique une tension suffisante, les électrons libres de la région n peuvent passer en région p, à travers la zone de déplétion, pour combler les trous. Mais, le plus souvent dans les semiconducteurs, au lieu d’utiliser une zone de déplétion comme barrière entre zones n et p, il est préféré un oxyde (le plus souvent de silicium lui aussi).

Le cas de la diode classique

Toutes les diodes modernes sont des composants semiconducteurs, au fonctionnement des plus simples.

Une diode classique, de redressement, est composée de zones p et n, avec une zone de déplétion intermédiaire (jonction PN). Quand il est appliqué une tension donnée à cette diode dans un circuit, si le – est du côté de la région N (et le + du côté de la région P), la diode est en polarisation directe, la barrière de potentiel de la zone de déplétion diminue et le courant passe. A l’inverse, si le + est du côté de la région N (et le – du côté de la région P), la polarisation est inverse : la barrière augmente et le courant ne passe pas.

Cependant, une diode classique peut se détruire en polarisation inverse si la tension devient trop grande. La diode Zener (que l’on sait utilisée contre les Courants induits géomagnétiquement – CIG) est conçue pour fonctionner en polarisation inverse et laisser passer le courant à partir d’un certain seuil de tension. Sans rentrer dans le détail, on les conçoit en agissant sur la taille de la zone de déplétion, généralement bien plus réduite et le niveau de dopage, généralement bien plus élevé que dans une diode classique. Ainsi, à partir d’un certain seuil de tension, au lieu de claquer comme une diode normale, les diodes Zener, en cascades, laissent passer le courant pour l’envoyer vers la terre et l’évacuer.

Fonctionnement de composants semiconducteurs CMOS

La technologie CMOS (Complementary Metal-Oxide Semiconductor) ou parfois appelée MOS est, de nos jours, la technologie la plus répandue en micro-électronique. Il convient au préalable de comprendre son fonctionnement en régime normal pour comprendre ensuite les impacts des radiations sur cette technologie.

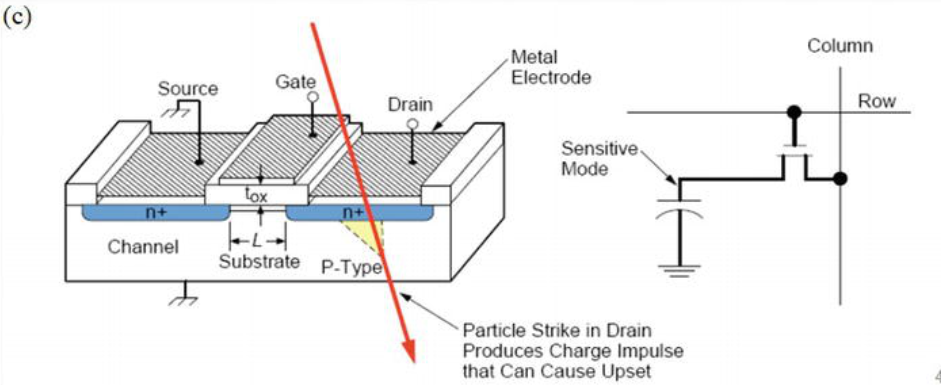

Transistors MOSFET et condensateurs des mémoires DRAM.

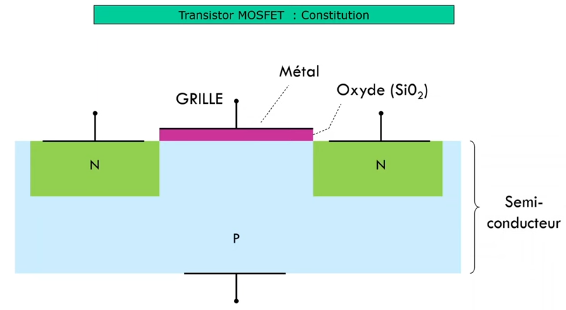

Ce sont des transistors à effet de champ, très utilisés. Il sont composés d’un substrat (la couche semiconductrice comme le silicium, plus ou moins dopée de type p), d’un isolant (un oxyde souvent de silicium), d’une source (région de type N qui fournit des électrons), d’un drain (région de type N qui les récupère) et d’une grille (ou gate), c’est à dire d’une électrode qui applique une tension sur un métal.

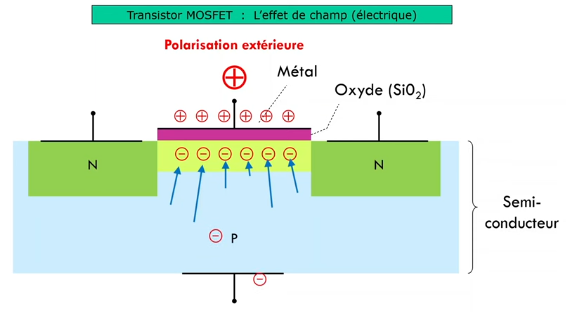

Quand une tension positive est appliquée via la grille sur le métal, un canal d’électrons se forme sous l’isolant, c’est à dire sous l’oxyde (ce sont des électrons issus du substrat mais aussi venant du coté négatif circuit), le courant passe alors entre les deux régions N (de la source vers le drain), le transistor est ainsi activé et le condensateur en sortie capte une charge, donc 1 bit (le condensateur n’est pas représenté sur le schéma). Si le courant ne passe pas dans le canal entre la source et le drain, c’est 0 bit dans le condensateur.

Plutôt que de créer un canal dans le substrat, on peut aussi faire entrer les électrons (propriété ondulatoire dont on passera tous les détails dans cet article) dans une couche isolante (comme un oxyde) et selon leur présence ou pas dans cette couche, avoir un bit ou pas.

MOSFET à mémoires Flash

On peut aussi piéger ces électrons dans une couche spéciale (floating gate), entre l’oxyde et la grille et la présence de ces électrons dans cette couche change la conductivité du transistor (0 bit). A l’inverse, si les électrons sont absents de cette couche spéciale, c’est 1 bit. Dans ce cas, il n’y a plus besoin du condensateur.

MOSFET à mémoire SRam

Dans le cas des mémoire SRam, il n’y a également plus besoin de condensateur pour stocker le bit mais d’un circuit de 6 MOSFET : 4 MOSFET (2 N-MOSFET et 2 P-MOSFET) pour maintenir une bascule en état stable en bits (0 ou 1) et 2 MOSFET pour lire et écrire l’état de cette bascule.

CMOS

Tout ce qui est appelé CMOS en électronique est constitué d’une paire de MOSFET. Un CMOS sert à mettre des portes logiques (ET / OU) dans les circuits mais ils peuvent aussi être utilisés comme résistances variables.

Thrysistors

Si les MOSFET sont utilisés pour les logiques et les mémoires à de très faibles puissances, les thrysistors sont utilisés pour les fonctions de commutation de puissance comme dans les convertisseurs de puissance ou dans la protection contre les surtensions. Ils sont donc conçus pour des tensions très élevées et reste « on » après un déclenchement. Ils réagissent comme des interrupteurs. Ils ont des structures de type P-N-P-N avec 3 jonctions P-N.

Autres semiconducteurs

Il y a d’autres composants semiconducteurs (BJT ou IGBT par exemple, aux propriétés différentes mais fonctionnant sur le même principe).

Tous ces composants semiconducteurs ont une vulnérabilité propre lorsqu’ils sont traversés par une particule ionisante qui crée des effets et anomalies spécifiques dans l’électronique de bord.

Les causes radiatives d’anomalies électroniques

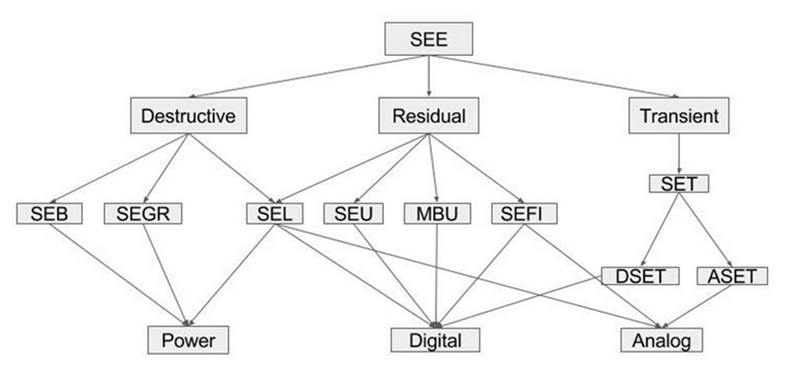

Les SEE (Single event effect – ou événement erroné singulier)

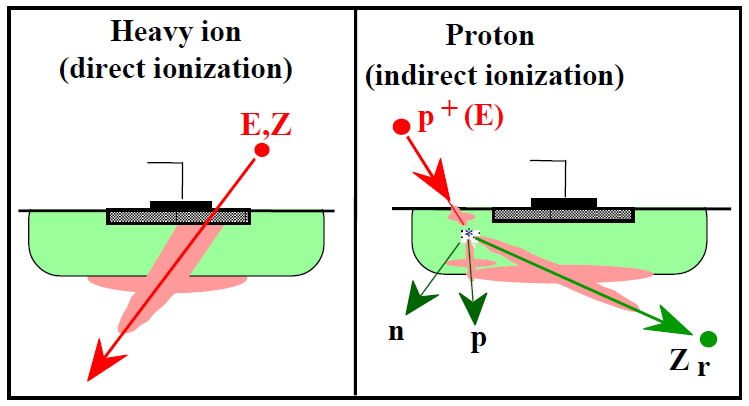

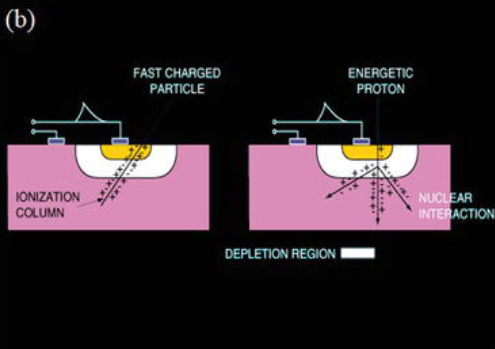

C’est la cause la plus documentée d’incidents techniques des satellites exposés aux radiations de l’espace. Les SEE sont généralement causés par deux types de sources : les rayons cosmiques (ionisation directe, notamment des ions lourds des RCG) ou les protons solaires (ionisation indirecte par les particules dégagées lors de la frappe du proton). A noter que certaines particules « piégés dans la magnétosphère » comme les ions lourds piégés (qui ont une faible énergie) et les électrons piégés (à faible masse) ne causent pas de SEE (sauf les électrons tueurs lors de fortes tempêtes géomagnétiques mais que l’on peut considérer comme des particules transitoires). Les éruptions solaires de particules (ESP, CME) sont les événements qui occasionnent le plus de SEE, surtout pour les engins spatiaux dans l’espace interplanétaire mais aussi pour ceux en orbite terrestre.

Notions physiques autour des SEE

Définition d’un SEE

Un SEE, c’est tout effet mesurable dans un circuit lié à l’impact d’un seul ion.

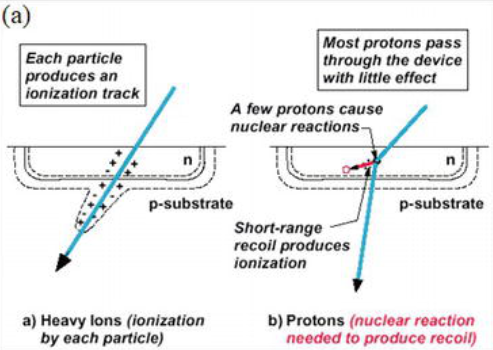

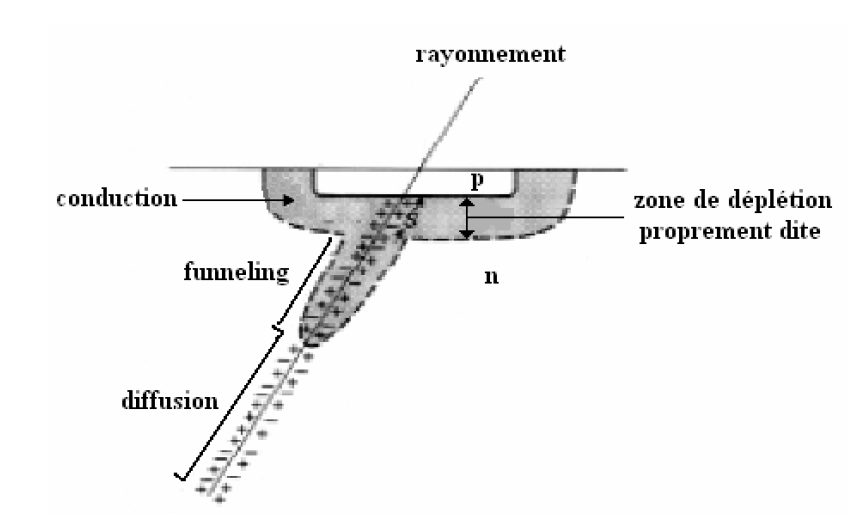

C’est le cas où un seul ion possède assez d’énergie pour avoir un effet à une échelle microscopique sur les matières qu’il traverse. Ce passage de l’ion se traduit par une injection élevée et localisée de charges par ionisation dans les matériaux d’un nœud sensible du circuit, créant des anomalies.

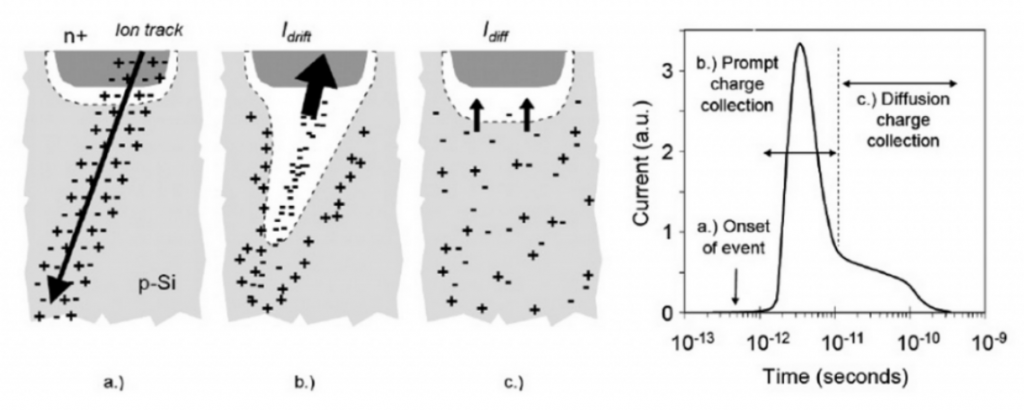

La particule créé sur son passage un ensemble de paires trou-électron et, pendant un temps très bref, peut rendre conductive la zone de déplétion le long de son trajet (funneling) alors que cette zone est normalement isolante . Le reste du trajet de la particule, dans le substrat et hors de la zone de déplétion, est nommé zone de diffusion, qui va participer elle aussi mais plus faiblement au courant temporaire et imprévu dans le semiconducteur.

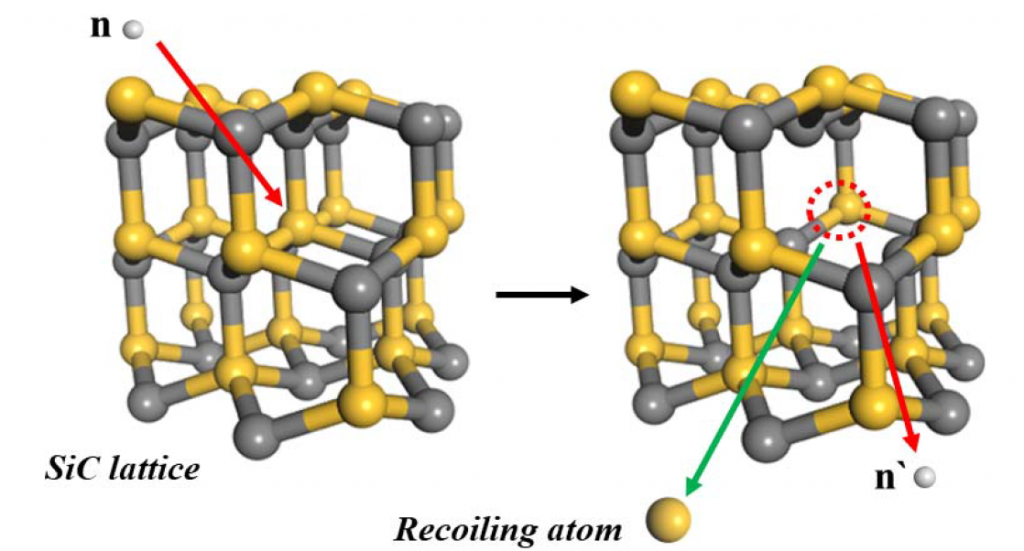

Le cas des impacts de neutrons dit ‘ »thermiques », donc de particules très énergétiques non chargés, dans le silicium est important pour l’électronique en environnement terrestre et surtout dans l’atmosphère traversée par les vols long courrier.

Certains neutrons thermiques très énergétiques produisent des atomes de recul, arrachés au composant, souvent lourds (C, Si, Mg et Al…) et qui génèrent des traces ionisantes à l’intérieur d’un MOSFET comme des paires trous/electrons dans l’oxyde ou le substrat.

Le LET : la mesure d’impact d’une particule dans une matière

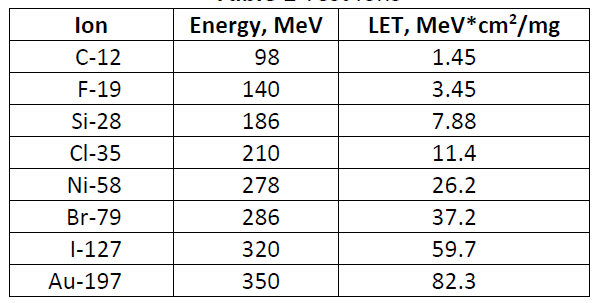

Pour mesurer l’impact de ces particules dans les matériaux, on utilise Le LET (« Linear Energy Transfer » ou « transfert linéique d’énergie »), c’est à dire une mesure de l’énergie déposée par unité de longueur lors du trajet d’une particule énergétique à travers un matériau. Elle se mesure en MeV*cm²/mg de matériel (par exemple dans le matériel d’un MOSFET, le silicium). Généralement, on fait des tests des composants électroniques candidats à l’espace dans des chambres sous vide depuis des laboratoires au sol en appliquant les fluences des particules énergétiques qu’on trouve dans les milieux radiatifs du Géo-espace.

Chaque ion utilisé dans un test a un LET connu dans un matériau (ex : un ion argon de 100 MeV a un LET de 15 MeV·cm²/mg dans le silicium).

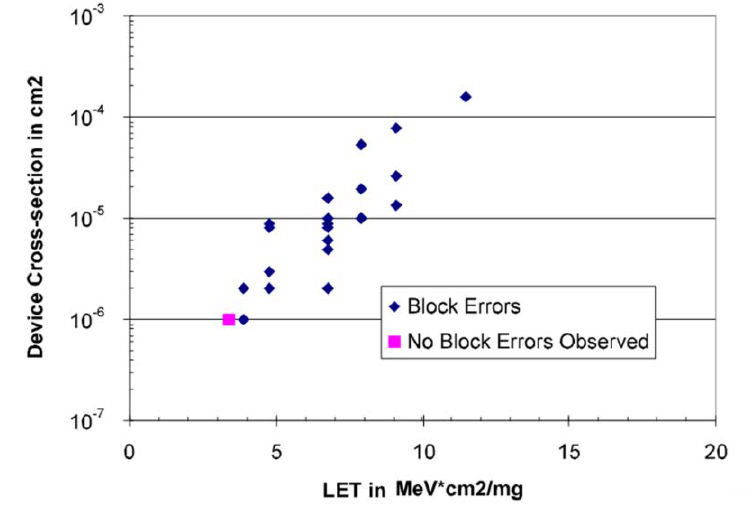

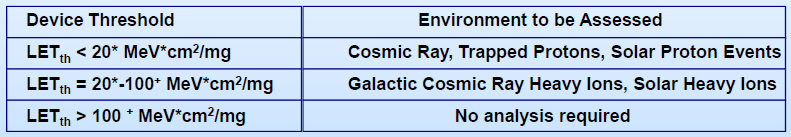

On applique à un composant une certaine fluence d’ions/cm² à ce LET. On observe les effets : erreurs, pannes… Ensuite on trace une courbe de section efficace avec le nombre de SEE par fluence, en fonction du LET pour en déduire le LETₜₕ (LET de seuil ; th pour threshold) c’est à dire le point à partir duquel des SEE commencent à apparaître et le LET de saturation, LET à partir duquel la section reste constante alors que le LET augmente. On en déduit alors la probabilité qu’un ion avec un LET donné cause un SEE (cross-section ou section efficace – en cm² ou en cm²/bit parfois pour les mémoires).

LETtho est donc le plus grand LET où aucun SEE ne se produit, généralement mesuré à une fluence standard. On considère que la matière testée est immune aux SEE si elle passe une fluence de 107 ions/cm2 sans SEE, selon les standards du JEDEC.

Seuils de LET entre « soft errors » et « hard errors » dans les SEE

La « soft error » est caractérisée lorsqu’une impulsion transitoire (SET – Single Event Transient) ou une d’une perturbation isolée (SEU – Single Event Upset comme une inversion de bits) se produit à l’intérieur du dispositif et provoque une erreur détectable à la sortie de ce dispositif mais sans dommages sur le composant ou le circuit. On calcule le SER (« Soft Error Rate » ou « taux d’erreurs numériques ») des composants en fonction des LET auxquels ils sont soumis.

L’immunité aux SEU est atteinte avec un LETₜₕ > 100. Cependant, un LETₜₕ de 37 est considéré comme un risque acceptable pour beaucoup de missions spatiales.

Les « hard errors« , ou erreurs matérielles, sont quant à elles physiquement destructrices pour le dispositif et entraînent des effets fonctionnels permanents, plus au moins importants selon leur taille et leurs effets systémiques.

Les SEE endommageant la matière des composants électroniques (SEB, SEGR que nous verrons après) sont testés à une fluence de 105 ions/cm2.

Si un RESET énergétique ne suffit pas à rétablir le composant, des systèmes de détection des erreurs et de correction des données (EDAC) et de redondances des composants (TMR : Triple Modular Redundancy) existent au sein des satellites pour une meilleure mitigation des SEE (le blindage seul n’est pas considéré comme une mitigation suffisante pour les protons de haute énergie > 30 MeV).

SEE avec effets non destructifs (soft error)

En moins d’1 milliseconde, le passage de la particule ionisante créé sur son trajet des paires trou-électron dans le substrat en silicone, dopé en p, en élargissant la zone de déplétion (a). Les électrons libérés s’agglomèrent dans la zone de déplétion élargie puis dérivent et s’accumulent dans le nœud de stockage, créant un courant bref relativement élevé (b). Puis les électrons restant dans le substrat continuent de se diffuser, plus lentement, vers le nœud, produisant alors un faible courant (c). Si le courant a été assez fort durant cette milliseconde, le nœud d’enregistrement du bit peut avoir changé d’état, produisant une erreur numérique (soft error) dans la mémoire du composant, comme par exemple un bit-flip dans un condensateur DRam.

Les SEU (Single Event Upset – Perturbation isolée par une particule ionisante)

La plupart des SEU proviennent des interactions nucléaires de protons à haute énergie et non par le biais d’un dépôt direct de protons ou de rayons cosmiques.

Au niveau des composants, par exemple, les chips mémoire Fairchild 93L422 présents dans le satellite d’observation Hubble, sont connus pour présenter régulièrement des SEU lorsqu’ils traversent l’anomalie de l’Atlantique sud.

Les SEU entraînent le plus souvent la corruption des mémoires.

Les bits-flips mémoires (SBU et MBU)

C’est un noeud de composant électronique (comme un drain de MOSFET) qui est impacté par une particule ionisante, directement ou à sa proximité directe. La charge libre causée à l’endroit de passage de la particule ionisante, comme des électrons éjectés lors de l’impact, provoque une erreur de fonctionnement du composant qui se traduit par une réécriture erronée de la mémoire ou une réinitialisation automatique du composant. On distingue dans les SEU : les SBU (Single bit upset : basculement d’un seul bit de la mémoire) et les MBU (Multiple Bit Upset : comme les SBU mais lorsque le rayonnement traverse plusieurs noeuds sensibles et affecte plusieurs bits). Dans ces cas, on parle de bit-flips.

Les SEFI (Single-event functional interrupt – interruptions de fonction temporaires et isolées)

Les plus sévères SEU entraînent des SEFI soit une interruption de fonction (Single-event functional interrupt – SEFI). Les SEFI mettent alors l’appareil en mode test, à l’arrêt ou dans un état indéfini. L’appareil ne fonctionnant pas normalement, il faut alors le redémarrer, voir le réinitialiser énergétiquement pour pouvoir le réutiliser correctement.

Les SET (Single event transient – pic isolé de tension)

C’est le cas où une particule énergétique traverse une jonction sensible dans le composant du semiconducteur (un canal dans un MOSFET, une jonction p-n dans une diode…), créant un pic de tension très temporaire, où les charges créées se dissipent en quelques centaines de nanosecondes, ne détruisant pas le composant. Son impact dépend du circuit et de la manière dont cet impact est capturé. Un SET peut, par exemple, perturber les circuits d’alimentation ou un capteur.

SEE avec effets destructifs (hard error ou DSEE – Destructive SEE)

SEHE (Single Event Hard Error – Erreurs matérielles permanentes et isolées)

Le SEHE est un SEE qui entraîne une modification permanente du fonctionnement d’un dispositif.

Stuck-bit (bit bloqué de façon permanente)

Il s’agit du cas où un bit est bloqué de façon permanente dans un dispositif de mémoire, même après un Reset ou une reprogrammation.

Block-error (erreur de bloc permanente).

Plus important encore, un « block error« , c’est le cas où un bloc entier de mémoire devient défectueux. Généralement, il est détecté quand trop d’erreurs surviennent dans une ligne ou dans une colonne d’une mémoire. Il peut être causé par une ligne de contrôle du bloc endommagée ou par un stuck-block (trop de cellules en stuck-bits sur une ligne ou colonne).

« SEHE » est généralement utilisé quand il n’est pas possible de classer une erreur dans un des mécanismes spécifiques ci-dessous :

Les SEL (Single Event Latch-Up – Blocage persistant par une particule ionisante)

Il s’agit d’un court circuit persistant se produisant entre la source d’alimentation et la masse dans un circuit intégré. Il peut provoquer des dysfonctionnements voir un endommagement des circuits intégrés. Les SEL ont généralement un LET élevé. Les SES (Single-Event Snapback) sont similaires aux SEL (courts-circuits) mais ils ne sont pas liés à la source d’alimentation globale du circuit et peuvent donc persister après la coupure d’alimentation, jusqu’à parfois griller le composant (SEB).

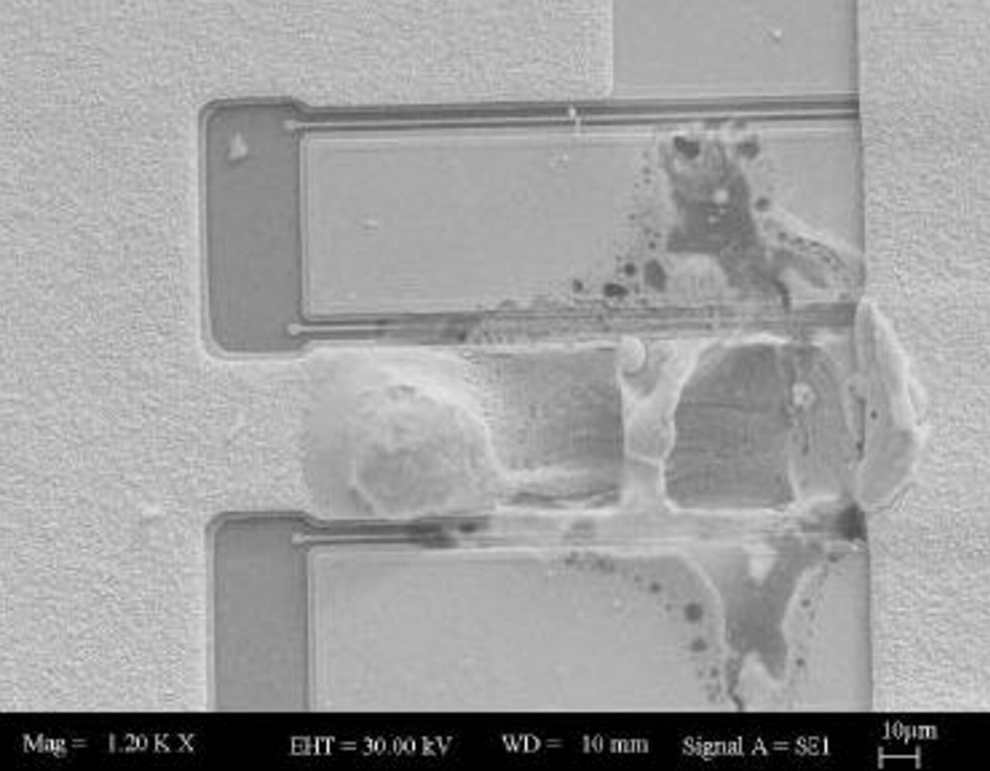

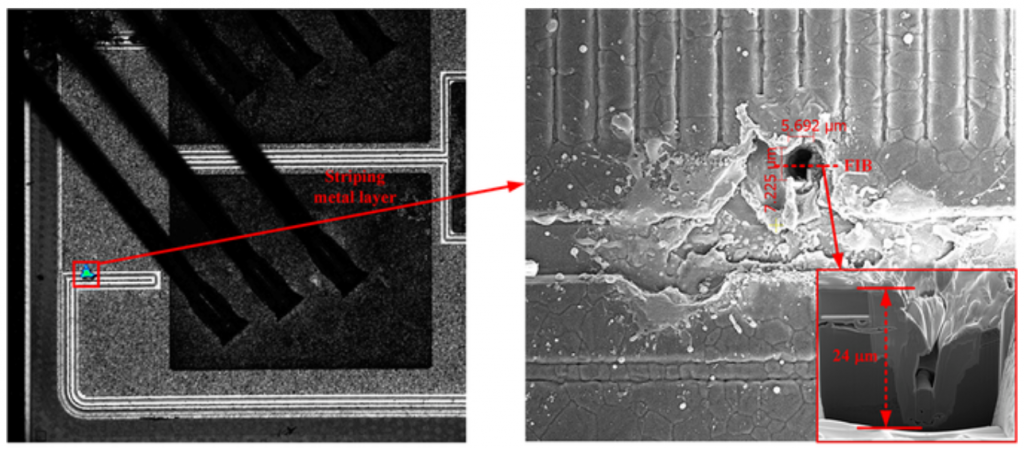

Les SEB (Single Event Burnout – Grillage d’un composant électronique par une particule ionisante).

C’est le cas où une particule pénètre un composant électronique, généralement un transistor de puissance, et y créé un état de courant élevé, dépassant sa plage de fonctionnement et le grillant. Les SEB ont généralement un LET très élevé, souvent issus d’un RCG.

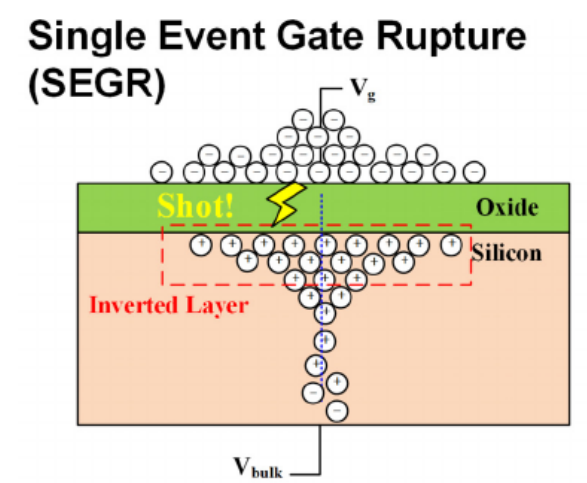

Les SEGR (Single Event Gate Rupture – Rupture de cheminement par une particule ionisante)

Les SEGR sont assez difficiles à distinguer des SEB. Ils ont néanmoins un mécanisme différent. Le SEGR est caractérisé par un passage d’une particule ionisante qui occasionne la rupture d’une interface isolante (rupture diélectrique dans l’oxyde) et la formation d’un nouveau chemin conducteur, ce qui entraîne une combustion destructrice. Il se produisent dans les MOSFET, les BJT et les CMOS mais concernent surtout les MOSFET d’alimentation en énergie. Les SEGR ont un LET très élevé. Les SEDR (Single-Event Diélectrique Rupture) concernent les composants non alimentant en énergie.

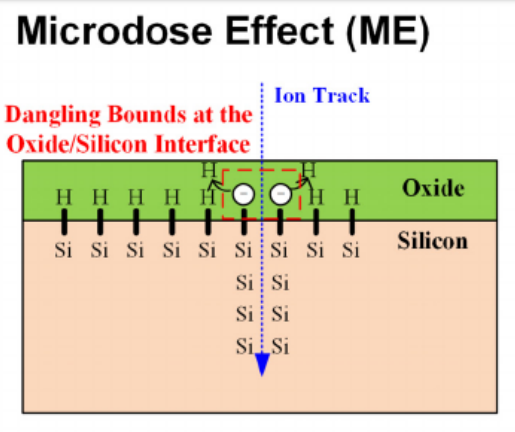

Les ME (Microdose effect ou effet microdose)

Les ME sont des SEE déclenchés lors du passage d’ions lourds au Let élevé dans les composants les plus miniaturisés. Il s’agit de zones de l’oxyde où les électrons éjectés lors de l’impact sont piégés soit par les impuretés de l’oxyde, soit, à l’interface oxyde/silicium, par les liaisons pendantes issus de la libération de l’hydrogène des liaisons SI-H lors de l’ionisation. Ils se limitent à des zones très limitées, à l’échelle nanométrique, et n’entraînent pas de rupture diélectrique de l’oxyde mais participent d’une dégradation progressive. Les ME modifient le champ électrique local, créent des courants de fuite et modifient les tensions de seuil des MOSFET. Le composant peut continuer à fonctionner mais en mode dégradé, ce qui peut aboutir à sa panne à long terme (stuck bit par exemple).

Résumé des effets des SEE

Les doses cumulées de radiations

Pour les satellites orbite GEO et MEO, la principale source de dose de radiations provient surtout des électrons de haute énergie piégés de la ceinture externe et, dans une moindre mesure, les protons solaires et RCG.

Pour ceux en orbite LEO, ce sont surtout les protons piégés de la ceinture intérieure de Van Allen, surtout au niveau de l’Anomalie de l’Atlantique Sud.

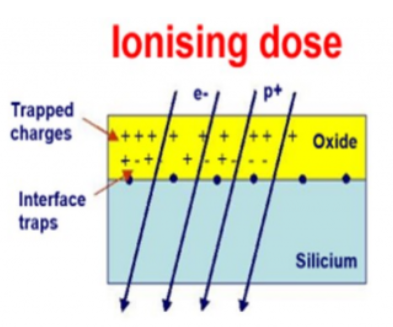

TID (Total ionising dose ou dose totale d’ionisation)

Notions physiques autour de la TID

La TID est l’accumulation, au cours de la mission, de la perte d’énergie due aux passages d’électrons, d’ions ou de protons dans la zone active d’un composant électronique, entraînant une dégradation par ionisation du composant et une réduction de performance au niveau du circuit ou du système, problématique sur le long terme (perte de systèmes critiques des engins spatiaux).

Cela peut produire une variété d’effets sur le dispositif tels que des décalages de la tension de seuil, des courants de fuite de surface et du bruit.

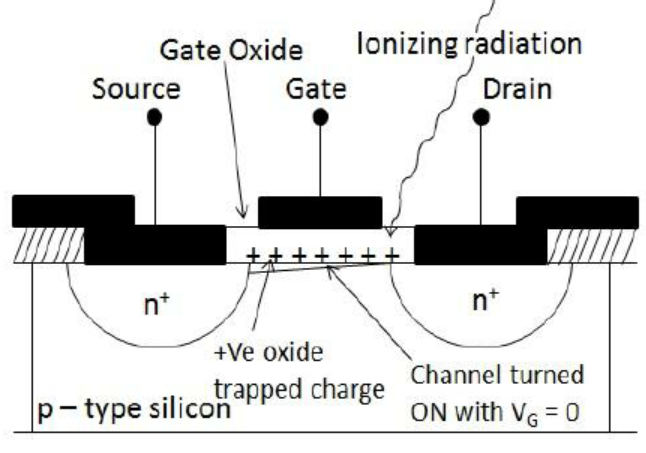

L’ionisation dans les couches isolantes (oxydes) des semiconducteurs entraîne une accumulation de charges positives piégées dans l’oxyde (des trous), à cause des électrons éjectés lors du passage de la particule. Ces trous se déplacent plus lentement, par sauts, et finissent pas être piégés (dans des imperfections du réseau cristallin de l’oxyde ou dans la zone de contact oxyde-substrat) mais loin des champs électriques émis par la grille, rendant difficile voir impossible la recombinaison des électrons extérieurs avec les zones de trous (car l’oxyde est avant tout un isolant).

La charge positive des trous piégés dans l’oxyde attire les électrons dans le canal du transistor et au contact oxyde/substrat, ce qui peut rendre le canal plus facile à activer, même sans tension sur la grille (voir schéma ci-dessus). De plus, l’accumulation de trous piégés dans l’oxyde peut créer des chemins conducteurs et donc des courants de fuite, diminuant la capacité isolante de l’oxyde.

Ainsi, si cette dose de charges positives devient trop élevée, le composant peut devenir complètement défectueux.

La TID s’exprime en Gray (unité Gy ou J/kg) ou plus anciennement en rad (1 Gray = 0,01 rad). En condition stable de rayonnement, la TID est donc le produit de la dose et du temps. Néanmoins, le flux de rayonnements n’étant pas constant, c’est la somme de toutes les doses absorbées dans le temps.

Des tests de composants aux radiations sont menés en laboratoire pour déterminer leur TDT (« Total dose tolerance » ou « tolérance de dose totale« ). Dans l’environnement, on mesure les TID grâce à des dosimètres.

Paramètres de dégradation des composants à différents niveaux de TID

llc : les courants de fuite

Comme nous venons de le voir, les radiations ionisantes créent des courants de fuite dans l’oxyde ou à l’interface oxyde/substrat. Pour mesurer ces courants de fuite, on mesure le courant consommé par le circuit à différents niveaux de radiations. Par exemple, si le llc d’un circuit CMOS passe de 10 µA à 1 mA après une TID à 100 krad, c’est le signe d’une dégradation sévère. De même, une hausse brève de llc après un événement radiatif peut être le signe d’un latch-up.

VOL ou VOH : Tension de sortie basse ou haute

VOL, c’est la mesure de la tension de sortie basse d’un MOS qui indique la capacité à produire un 0 logique. A l’inverse, VOH, c’est la mesure de la tension de sortie haute d’un MOS qui indique sa capacité à produire un 1 logique. Une augmentation du VOL ou une diminution du VOH indique que le MOS peut être plus susceptible d’erreurs logiques dans le circuit, par exemple dans l’attribution des bits, s’il dépasse les tensions de seuil VOL ou VOH.

ILL ou ILH : courant d’entrée bas ou courant d’entrée haut

A l’inverse de VOL et VOH, ILL et ILH mesurent le courant à la broche d’entrée d’un MOS. Il est quantifié en microampères et a pour but de détecter les courants de fuite du MOS (liés eux aussi à l’ionisation de l’oxyde de grille). Il mesure donc la qualité de l’isolation de l’oxyde aux entrées. Si ILL et ILH augmente trop après une dose de radiations, il peuvent créer des fuites dans le canal et le MOS produit alors des erreurs logiques.

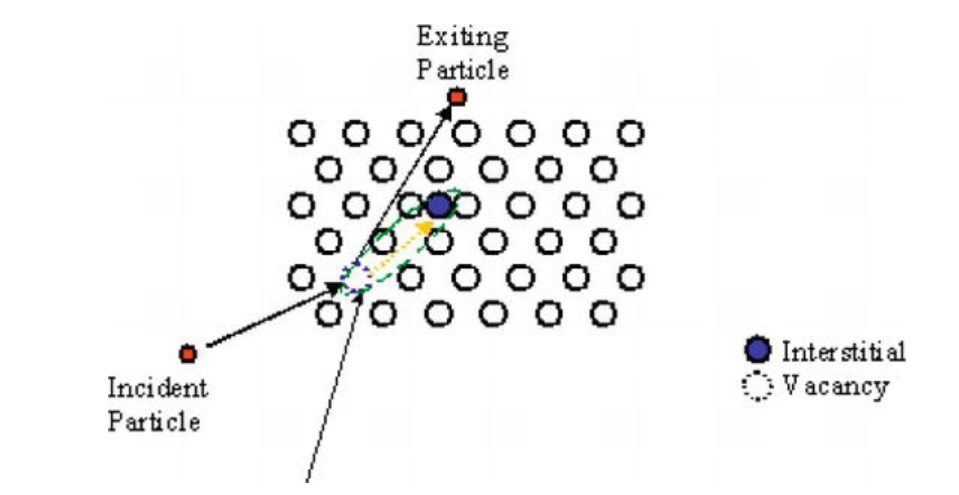

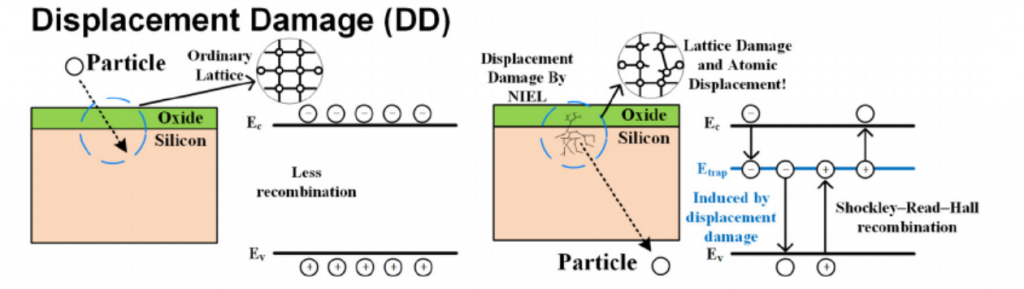

DDD (Displacement Damage Dose ou dose de dommages par déplacements) ou TNID

Similaire à la TID, la DDD est la dégradation cumulative mais non ionisante liée aux déplacements des atomes d’un réseau cristallin semiconducteur par rapport à leur position dans ce réseau. C’est pour cette raison que la DDD est aussi nommée TNID (« Total Non-Ionising Dose » ou « dose totale non ionisante »). Au cours de la mission ou lors d’un événement fort de rayonnements, un déplacement suffisant peut se produire et modifier les propriétés de performance du dispositif ou du matériau.

Les particules énergétiques susceptibles d’avoir des effets de déplacement sur les matériaux semiconducteurs sont les neutrons, les protons, les électrons, les particules alpha et les ions lourds. Les électrons secondaires, produits par des photons très énergétiques, peuvent également engendrer des effets de déplacement.

Par exemple, un DD (dommage par déplacement d’atomes) peut être lié à une particule énergétique qui endommage le silicone des transistors et créer un piège pour la conductivité et les valences. Plus il y a de DD (DDD), plus la durée de vie des composants est réduite. La DDD entraîne par exemple une dégradation des cellules des panneaux solaires des satellites.

Autres effets des doses radiatives cumulées

L’augmentation du bruit de fond dans les instruments

Il existe un bruit constamment présent dans la matériaux électroniques, dit « bruit de scintillation » liés aux impuretés dans le silicium ou aux recombinaisons des paires trous-électrons parasites, qui affecte la qualité des capteurs. Un environnement radiatif de plus en plus intense, cause donc davantage de bruit de scintillation, par exemple sur les images des capteurs CCD, très utilisés en astronomie.

Sur les matériaux non liés à l’électronique

Il n’y a pas que la microélectronique et les capteurs qui sont impactés par les radiations ionisantes mais aussi certains matériaux comme les polymères (comme les couvertures thermiques) et les matériaux optiques (comme les verres de silice et autres cristaux).

Le chargement interne ou de surface : le rôle indirect des radiations

Les chargements internes et de surfaces mènent à des décharges électrostatiques qui peuvent endommager les matériaux et composants des satellites, surtout les panneaux photovoltaïques.

Bien que ces phénomènes soient une conséquence du dépôt et de l’accumulation de particules radiatives, (principalement des électrons) dans les matériaux et que la TID peut jouer un facteur facilitant ces anomalies, ni l’ECSS (European Cooperation for Space Standardization), ni la NASA ne traitent ces anomalies dans les causes radiatives des défaillances des satellites.

En effet, le dépôt et l’accumulation d’électrons dans les satellites n’est pas forcément endommageant pour les satellites. Ce sont les décharges électriques, dans certaines conditions électrostatiques, qui le sont et bien d’autres facteurs entrent en jeu dans l’apparition de ces décharges électriques si bien que les radiations ne sont qu’un facteur secondaire dans l’occurrence de ces phénomènes.

Conclusion

Résumé des effets électroniques des radiations dans l’espace, en altitude et au sol

Les perturbations des radiations dans l’électronique à semiconducteurs sont donc de deux types : les SEE (effets transitoires ou ponctuels liés au passage d’une unique particule) et les effets de dose cumulée à savoir la TID (effets de dose résultants de l’ionisation des isolants), la DDD (effets de dose de déplacement d’atomes) et l’augmentation du bruit de scintillation. Dans l’environnement spatial, les composants électroniques sont affectés par tous ces phénomènes, alors que dans l’environnement atmosphérique de la troposphère et, dans une bien moindre mesure, au niveau du sol, les effets de dose ou de déplacement sont négligeables et seuls les SEE ont un impact opérationnel. Ils sont liés aux rayonnements cosmiques qui, en traversant notre atmosphère, se décomposent en particules secondaires dont les neutrons, dits “thermiques”, les plus importants.

L’accroissement de la vulnérabilité des systèmes avec la miniaturisation et la généralisation des composants semiconducteurs

La miniaturisation croissante des composants électroniques semiconducteurs et leurs déploiements à vaste échelle dans des domaines variés conduit à davantages de dysfonctionnements ; la taille nanométrique atteinte par les composants comme les transistors augmente leur densité par unité de surface. De ce fait, le passage d’une seule particule ionisante peut à elle seule impacter beaucoup plus de transistors et autres composants CMOS que dans les technologies précédentes, ce qui oblige les systèmes embarqués de correction d’erreurs, de redondances et de blindage à être de plus en plus en complexes. Ainsi, cette miniaturisation à vaste échelle des composants électroniques rend plus probable les risques dans les systèmes aérospatiaux embarqués mais aussi dans les systèmes au sol ; risques qui pourraient passer de négligeables à faibles et ainsi impacter la sécurité de beaucoup de systèmes.

La technologie quantique au défi des interférences des rayons cosmiques.

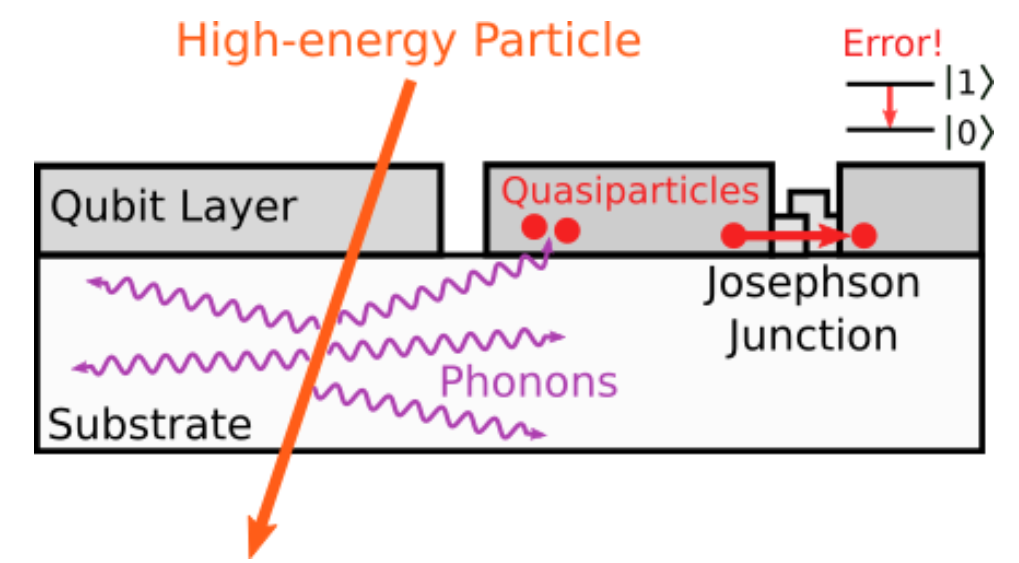

Dans un proche avenir, la technologie des semiconducteurs va ce coupler avec celle des puces et mémoires quantiques de technologie supraconductrice, que nous n’avons pas aborder ici dans un article encore très long.

Ainsi, comme la technologie semiconductrice subiste dans les systèmes embarqués, ses vulnérabilités subsisteront elles aussi et, dans un proche avenir, il faudra rajouter les vulnérabilités liées à la technologie quantique supraconductrice, totalement différentes (LET et SEE n’ont plus aucun sens dans cette technologie). De plus, d’autres particules et ondes habituellement sans effets sur les composants CMOS ont un impact significatif dans celles des supraconducteurs quantiques (photons énergétiques, muons et quasi-particules ou encore les ondes comme les phonons, rayons X et Gama).

Néanmoins, les interférences sur la technologie quantique supraconductrice, quelles soient liées aux particules et ondes cosmiques secondaires, aux rayonnements solaires et naturels, ou à d’autres sources technologiques au sol, sont déjà un challenge en temps normal pour la recherche appliquée. En environnement terrestre au sol, les processeurs quantiques doivent être fortement blindés, notamment dans des cryostats de 1 à 2 m de haut, les plus imperméables possible à ces interférences. De plus, ils doivent corriger automatiquement les erreurs causées par certaines fluctuations de leur milieu. Si la problématique des quasi-particules impliquées dans les rafales d’erreurs pourrait être résolue résolue par l’ajout du fine couche d’alumium dans les jonctions Josephson, jouant un rôle de filtre, il reste que les particules à haute énergie dégradent le substrat et augmente le bruit dans le circuit, ce qui reste encore un défi important.

Dans le prochain article, nous traiterons des effets macroscopiques de ces radiations dans les systèmes embarqués (anomalies, incidents, pannes, interruptions de mission, voir sorties extra-véhiculaires dans l’espace pour réparer ces pannes).

Je reste à la disposition pour compléter ou corriger cet article à l’intention de ceux qui souhaiterait l’améliorer.

Annexes

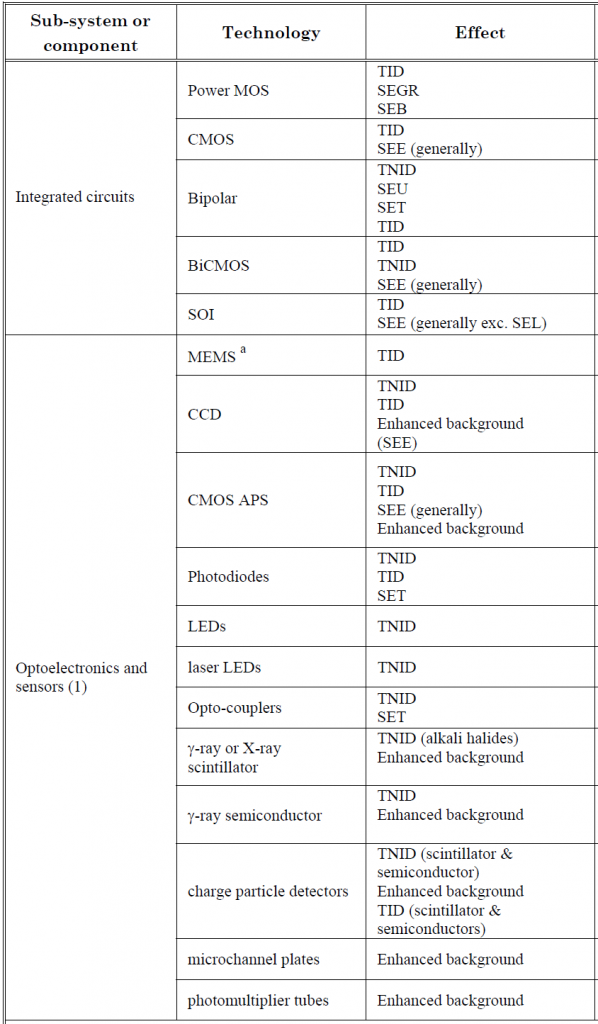

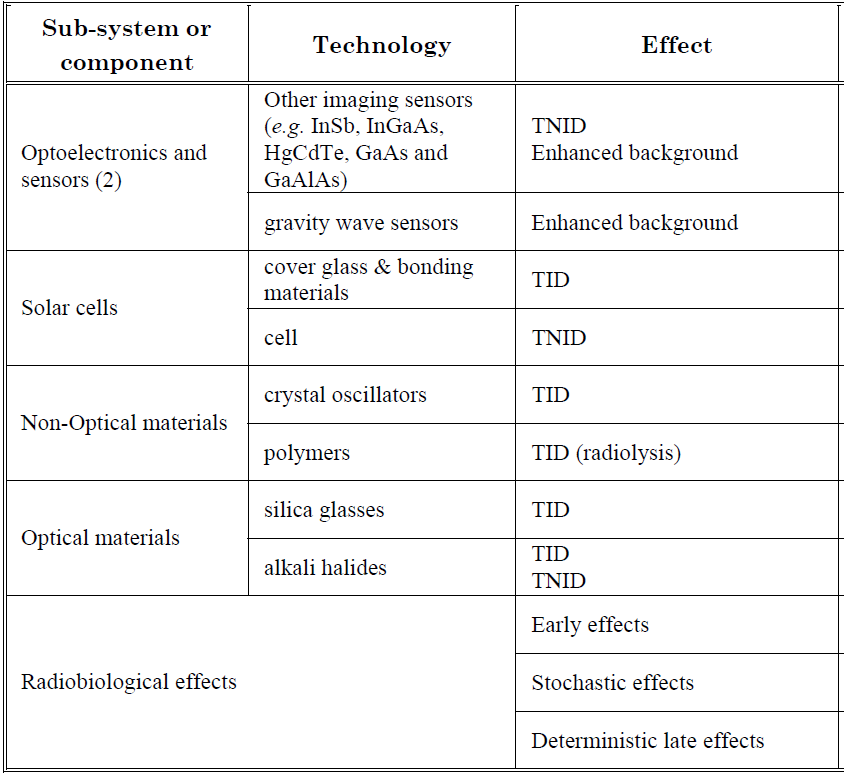

Effet des radiations sur les composants et sous-systèmes (ECSS-E-HB-10-12A)

Base de données/modélisations (SEE/TID/DDE)

Calculateur de flux de neutons au sol (norme JESD89A)

SPENVIS – Modélisation des sources de radiations spatiales et des effets des radiations

NTRS – NASA Tedchnical Reports Server

Bibliographie

Documents de standardisation

ECSS. « ECSS-E-HB-10-12A – Calculation of radiation and its effects and margin policy handbook » 17 December 2010.

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION « Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor Devices« . JESD89A. 2006.

Articles scientifiques et thèses

Hands, A. D. P., Ryden, K. A., Meredith, N. P., Glauert, S. A., & Horne, R. B. (2018). Radiation effects on satellites during extreme space weather events. Space Weather, 16, 1216–1226. https://doi.org/10.1029/2018SW001913

Peng, Chao & Lei, Zhifeng & Chen, Ziwen & Yue, Shaozhong & Zhang, Zhangang & He, Yujuan & Huang, Yun. (2021). Experimental and simulation studies of radiation‐induced single event burnout in SiC‐based power MOSFETs. IET Power Electronics. 14. 10.1049/pel2.12147.

Matt, Mahesh & Patel, Raghu & Shivappa, Naveen & Mrudula, K. & Jeetendra, Shailaja & Sanjeev, Ganesh. (2014). Transconductance and Transfer characteristics of 8 MeV Electron Irradiated Dual N-channel MOSFETs. International Journal of Emerging Technology and Advanced Engineering. 4. 247-250.

Sun, Qian & Chi, Yaqing & Guo, Yang & Liang, Bin & Tao, Ming & Wu, Zhenyu & Guo, Hongxia & Zheng, Qiwen & Chen, Wangyong & Gao, Yulin & Zhao, Peixiong & Li, Xingji & Chen, Jianjun & Luo, Deng & Sun, Hanhan & Fang, Yahao. (2024). Gate breakdown induced stuck bits in sub-20 nm FinFET SRAM. Applied Physics Letters. 125. 10.1063/5.0214621.

Kenneth A. LaBel « Single Event Effects. Specific Approach« . NASA. 2013.

Victor U. J. Nwankwo, Nnamdi N. Jibiri and Michael T. Kio. « The Impact of Space Radiation Environment on Satellites Operation in Near-Earth Space« . InterchOpen. 2020

P. Peronnard. « Méthodes et outils pour l’évaluation de la sensibilité de circuits intégrés avancés face

aux radiations naturelles« . Thèse. Sciences de l’ingénieur [physics]. Université Joseph-Fourier – Grenoble I. 110 p. 2009. Français. NNT : tel-00481742.

Matt McEwen « Resolving High-Energy Impacts on Quantum Processors« . Research Google Blog. 2022.

McEwen, Matt, et al. « Resisting high-energy impact events through gap engineering in superconducting qubit arrays. » Physical Review Letters 133.24 (2024): 240601.

C. Martinella et al. « Impact of Terrestrial Neutrons on the Reliability of SiC VD-MOSFET Technologies« .

IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 68, NO. 5, MAY 2021

Vidéos

Hervé Discours « Principe de fonctionnement d’un transistor MOSFET ». YouTube. 2024.